Simulation

avec LTspice IV

Simulation

avec LTspice IV

Etude de l'impédance

- d'un circuit RLC parallèle

- d'un quartz d'horlogerie 32768 Hz

Nous allons simuler l'impédance Z et le déphasage φu/i en fonction de la fréquence.

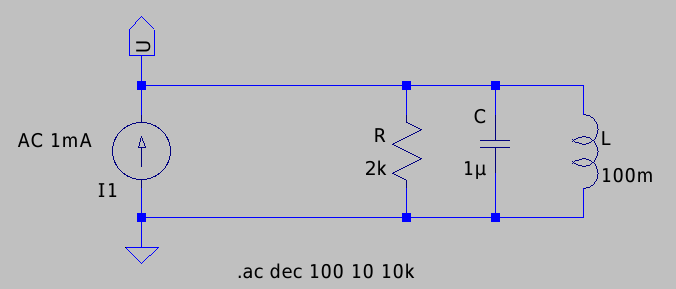

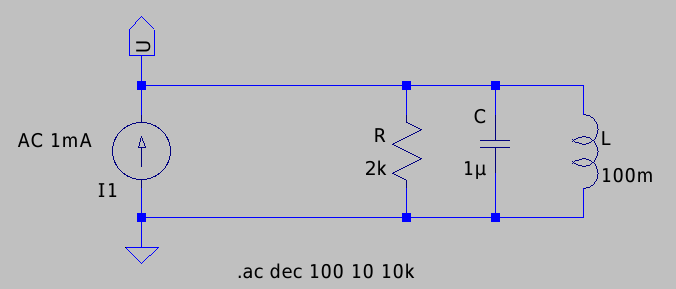

1. Impédance d'un circuit RLC parallèle

1.1. Saisie du schéma

1.2. Simulation

Simulate -> Edit Simulation Cmd :

AC Analysis :

Type of Sweep : Decade

Start Frequency : 10

Stop Frequency : 10k

On lance la simulation (Simulate -> Run) :

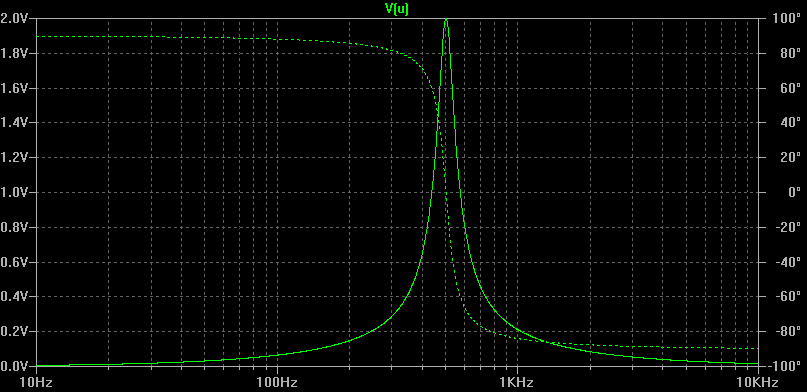

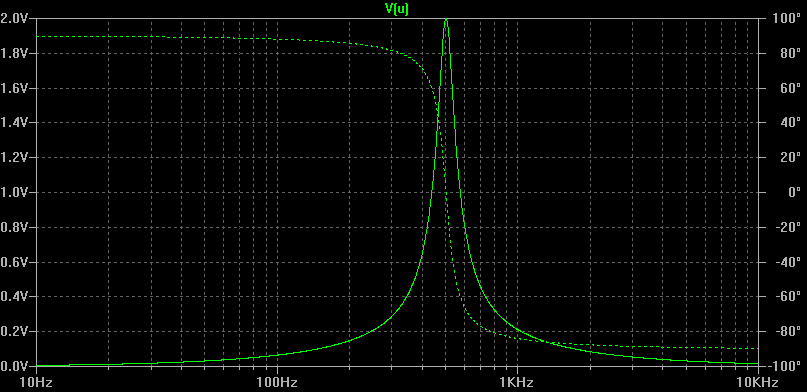

La tension u est l'image de l'impédance.

Avec une source de courant de 1 mA, 1 V donne 1 kΩ.

On constante que l'impédance maximale correspond à R (soit 2 kΩ).

La fréquence est alors 503 Hz [en théorie : 1/(2π√(LC))], le déphasage est nul (tension et courant en phase).

En basse fréquence, le déphasage tend vers +90° (comportement purement inductif L).

En haute fréquence, le déphasage tend vers -90° (comportement purement capacitif C).

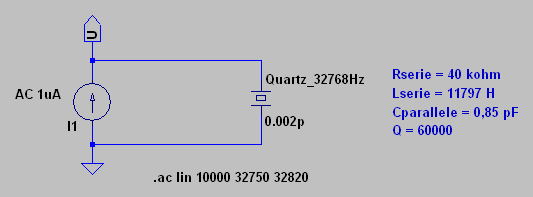

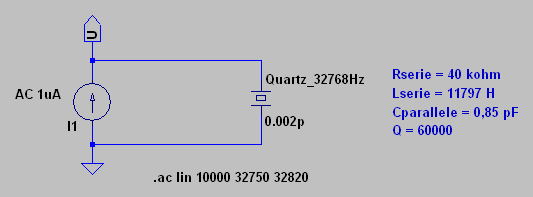

2. Impédance d'un quartz d'horlogerie 32768 Hz

2.1. Saisie du schéma

Le modèle équivalent de ce quartz est :

C = 2 fF = 0,002 pF

R série = 40 kΩ

L série = 11 797 H

C parallèle = 0,85 pF

Le facteur de qualité est : Q = Lω/R = 60 000

Bibliographie : http://fr.wikipedia.org/wiki/Quartz

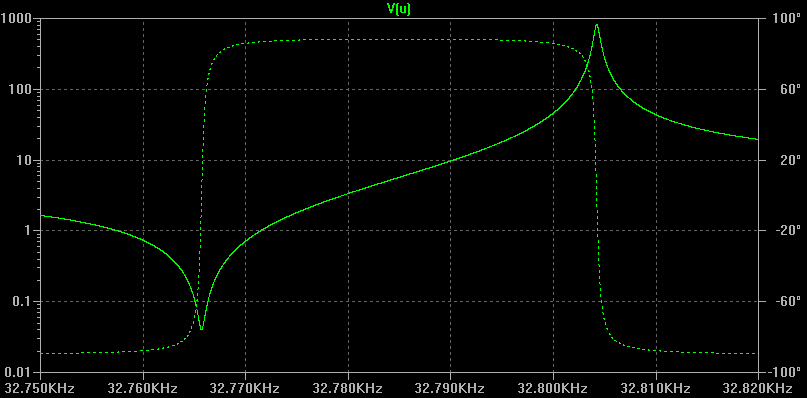

2.2. Simulation

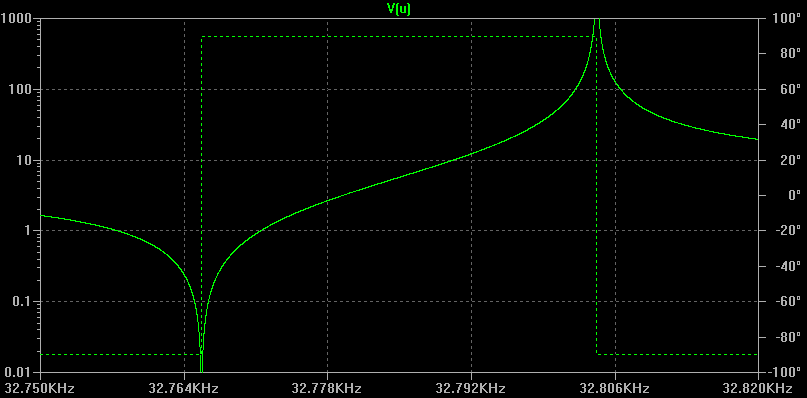

La tension u est l'image de l'impédance.

Avec une source de courant de 1 µA, 1 V correspond à 1 MΩ :

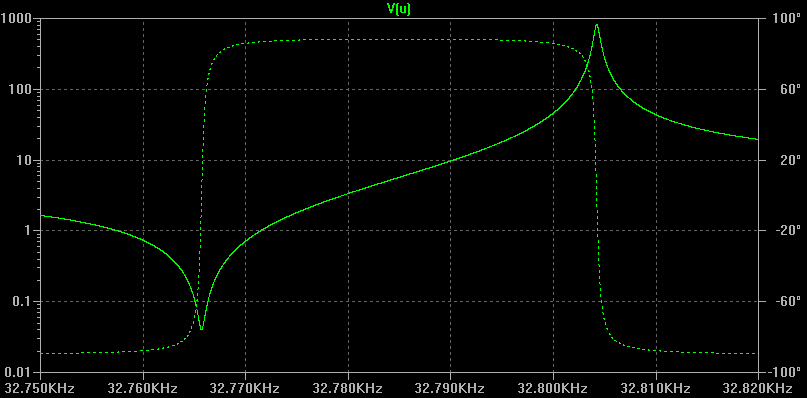

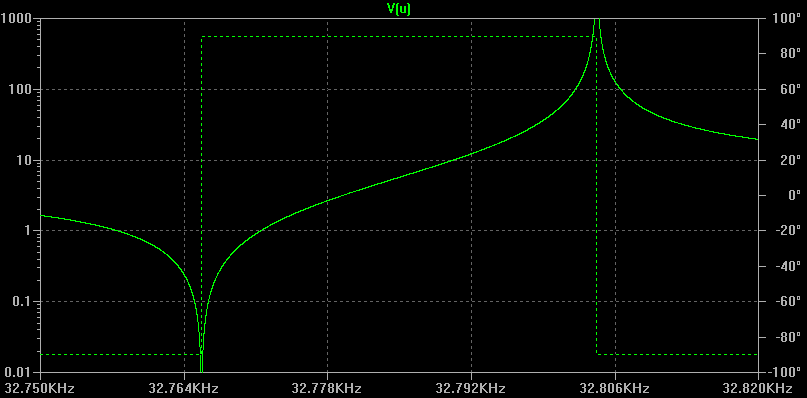

On peut simplifier le modèle en négligeant la résistance R série :

La fréquence de résonance série est 32766 Hz (impédance minimale).

La fréquence de résonance parallèle est 32804 Hz (impédance maximale).

Dans la plage [ 32766 - 32804 Hz ], le quartz est inductif (déphasage +90°).

En dehors de cette plage, le quartz est capacitif (déphasage -90°).

Télécharger ces projets LTspice IV

(C) Fabrice Sincère ; Révision 1.1.3