Simulation

avec LTspice IV

Simulation

avec LTspice IV

- Modulation de fréquence

numérique FSK

- Démodulation FSK avec une PLL (boucle à verrouillage de phase)

Nous allons simuler la modulation et la démodulation FSK

(Frequency-Shift Keying) avec le logiciel gratuit LTspice

IV.

1. Saisie du schéma

1.1. Modulation FSK

Le signal d'entrée est un signal binaire 0 V / 1 V aléatoire (débit : 500

bits/s) :

Edit -> Component : bv (arbitrary behavioral voltage

source)

Value : V=rand(time*500) >= .5

Le signal d'entrée est ensuite modulé :

Edit -> Component : modulate (modulateur FM)

Value : mark=1100 space=900

0 logique (0 V) -> 900 Hz (sinus ± 1 V)

1 logique (1 V) -> 1100 Hz (sinus ± 1 V)

On obtient ainsi une modulation FSK (1000 ± 100 Hz).

1.2. Démodulation FSK avec une PLL

La boucle à verrouillage de phase (PLL : Phase Lock Loop) est un

asservissement de phase.

La PLL est constituée de 3 éléments :

- une porte logique ou exclusif (comparateur de phase)

- un filtre passe-bas (R1 et C1, constante de temps 1 ms)

- un oscillateur commandé en tension (VCO : Voltage Controlled

Oscillator)

Edit -> Component : xor (porte logique ou exclusif)

Value : ref=0V

En entrée de la porte logique :

- 0 logique si v < Vref

- 1 logique si v > Vref

En sortie de la porte logique :

- 0 logique -> 0 V

- 1 logique -> 1 V

Edit -> Component : modulate (VCO linéaire)

Value : mark=2000 space=0

0 V donne 0 Hz

1 V donne 2000 Hz

0,5 V donne 1000 Hz

0,45 V donne 900 Hz

0,55 V donne 1100 Hz...

La mise en forme du signal démodulé nécessite :

- un filtre passe-bas (R2 et C2, constante de temps 0,5 ms)

- un trigger de Schmitt

Edit -> Component : schmtbuf (trigger de Schmitt non inverseur)

Value : Vt=.5V Vh=0.01V

Les tensions de seuil du trigger sont :

- 0,5 + 0,01 = 0,51 V

- 0,5 - 0,01 = 0,49 V

2. Simulation

Simulate -> Edit Simulation Cmd :

Transient : Stop Time : 100 ms

On lance la simulation (Simulate -> Run) :

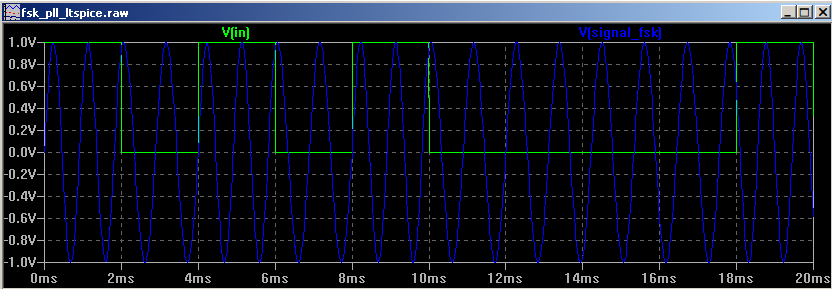

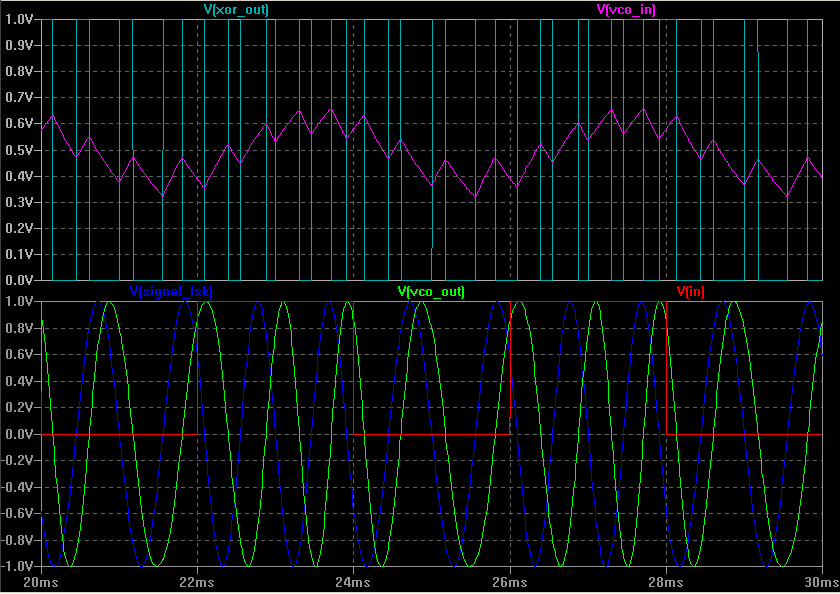

La modulation FSK :

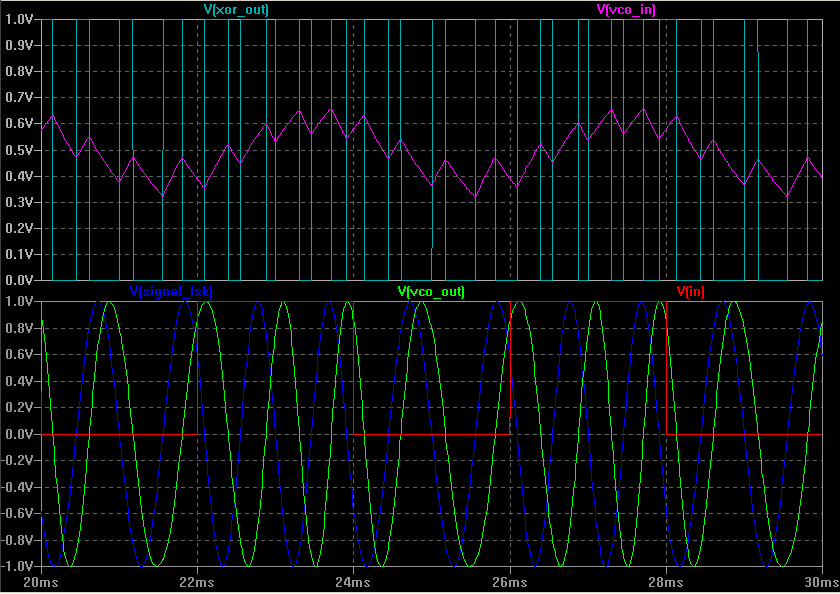

La boucle à verrouillage de phase :

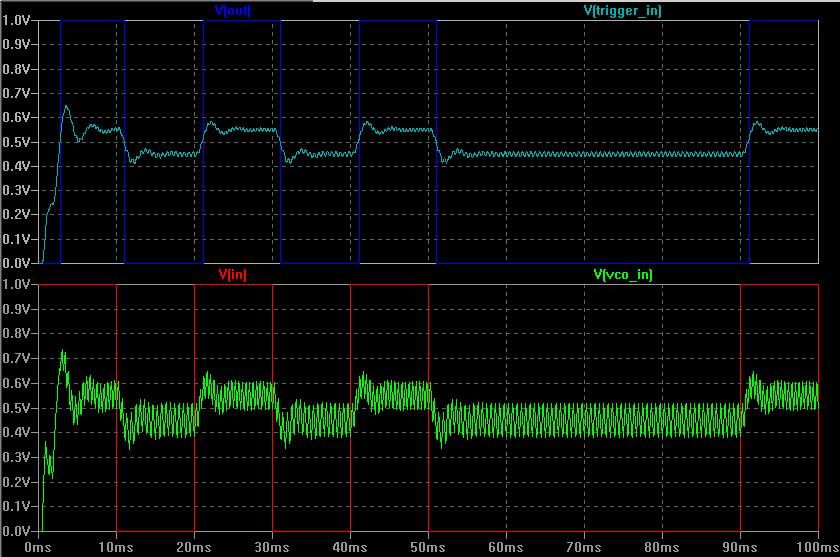

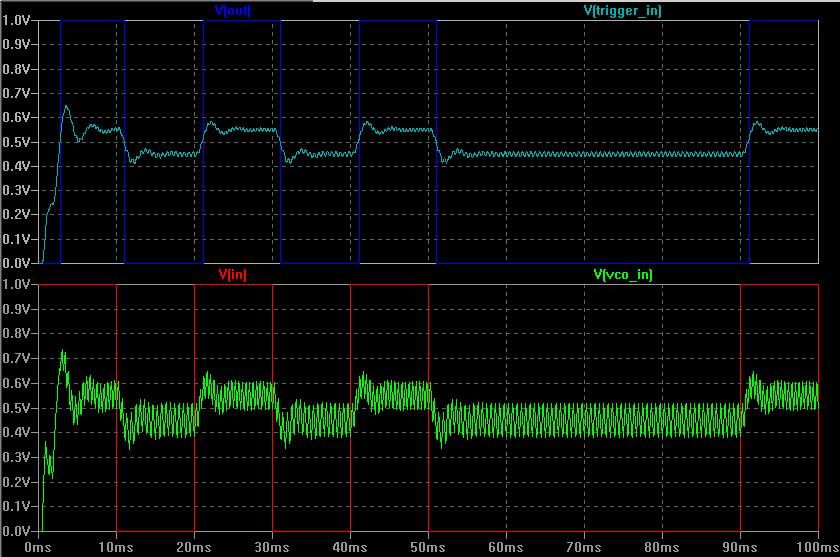

Comparaison des signaux Vout et Vin :

3. Simulation n°2

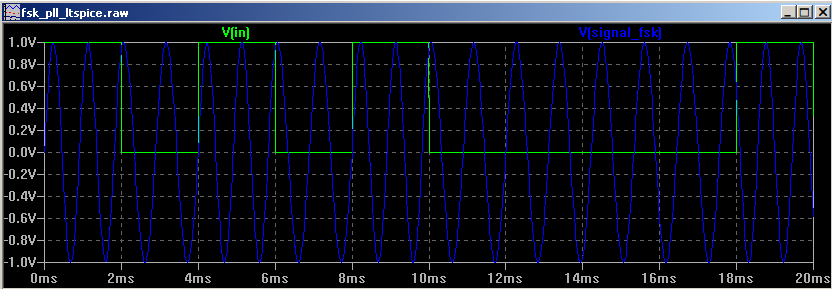

La même chose avec un débit de 100 bits/s (au lieu de 500 bits/s) :

Télécharger ces projets LTspice IV

(C) Fabrice Sincère ; Révision 1.1.3