Simulation

avec LTspice IV

Simulation

avec LTspice IV

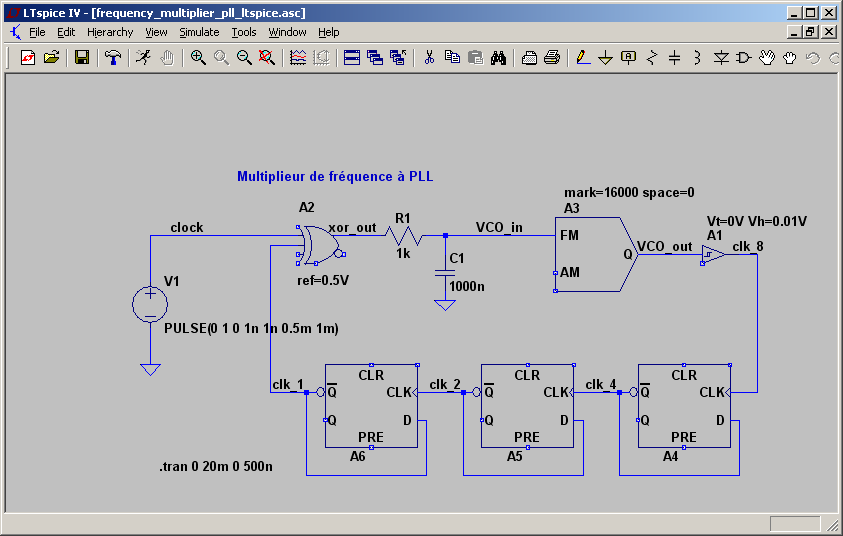

- Multiplieur de fréquence avec une PLL (boucle à verrouillage de phase)

Voici un exemple où nous allons multiplier par 2, 4 et 8 la fréquence d'une horloge grâce à une PLL.

1. Saisie du schéma

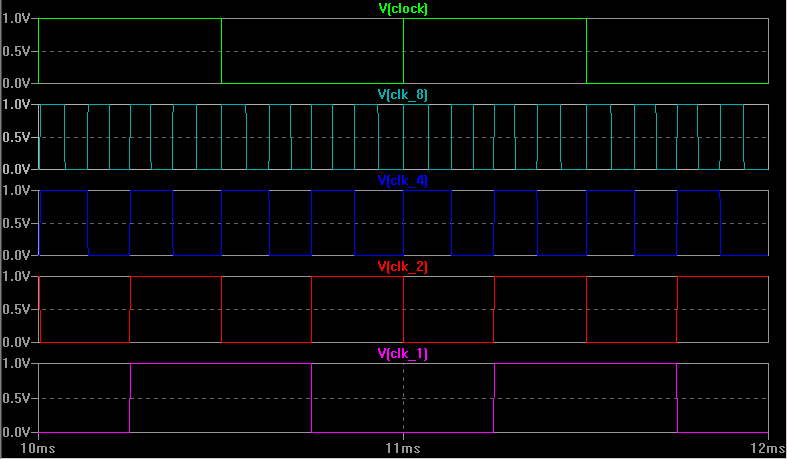

L'horloge de base (0 V / 1 V) a une fréquence f = 1 kHz.

Par la suite, un niveau logique 0 correspond à 0 V et un niveau logique 1 correspond à 1 V.

La boucle à verrouillage de phase (PLL : Phase Lock Loop) est un

asservissement de phase.

La PLL est constituée de 3 éléments :

- une porte logique ou exclusif (comparateur de phase)

- un filtre passe-bas (R1 et C1, constante de temps 1 ms)

- un oscillateur commandé en tension (VCO : Voltage Controlled

Oscillator)

Dans la chaîne de retour, on place 3 diviseurs de fréquence par 2 (à base de bascules logiques de type D).

On divise ainsi la fréquence par 8.

Edit -> Component : xor (porte logique ou exclusif)

Value : ref=0.5V

En entrée de la porte logique :

- 0 logique si v < 0,5 V

- 1 logique si v > 0,5 V

En sortie de la porte logique :

- 0 logique -> 0 V

- 1 logique -> 1 V

Edit -> Component : modulate (VCO linéaire)

Value : mark=16000 space=0

0 V donne 0 Hz

1 V donne 16 kHz

0,5 V donne 8 kHz (soit 8 fois la fréquence de l'horloge de base)...

La sortie du VCO est sinusoïdale (amplitude ± 1 V).

Un trigger de Schmitt permet de mettre en forme ce signal.

Edit -> Component : schmtbuf (trigger de Schmitt non inverseur)

Value : Vt=0V Vh=0.01V

Les tensions de seuil du trigger sont donc :

- 0 + 0,01 = 0,01 V

- 0 - 0,01 = -0,01 V

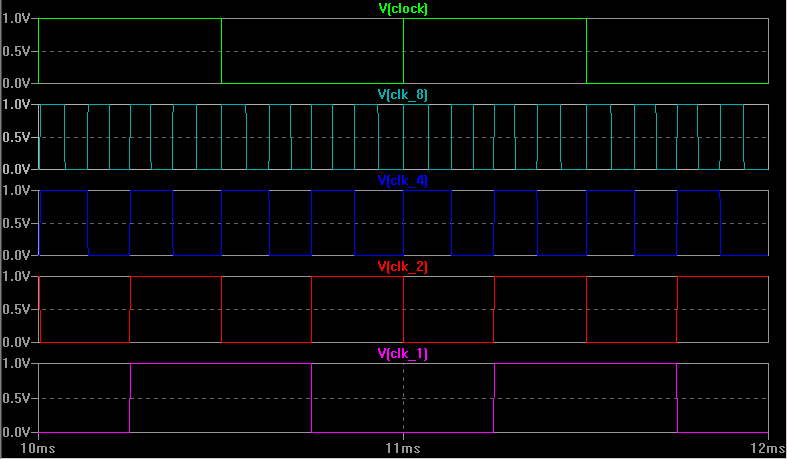

2. Simulation

Simulate -> Edit Simulation Cmd :

Transient : Stop Time : 20 ms

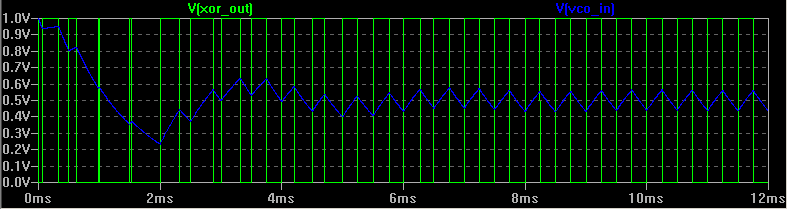

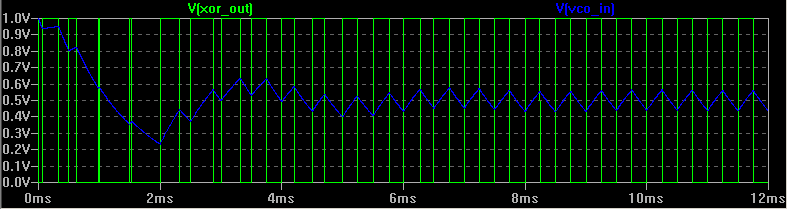

On lance la simulation (Simulate -> Run) :

On voit qu'à partir d'une horloge de fréquence f (1 kHz), on obtient les fréquences multiples 2f, 4f et 8f (2, 4 et 8 kHz).

On remarque que le régime transitoire dure environ 6 ms :

Cette technique est très utilisée.

Dans votre ordinateur, vous avez une PLL qui permet d'obtenir, à partir

d'un oscillateur à quartz (plusieurs dizaines de MHz), une fréquence d'horloge beaucoup plus grande

(plusieurs centaines de MHz).

Il faut aller dans le BIOS pour accéder aux paramètres de cette PLL.

Télécharger ce projet LTspice IV

© Fabrice Sincère ; Révision 1.4.2

Cette œuvre est mise à disposition selon les termes de la Licence Creative Commons - Attribution - Pas d'utilisation commerciale - Partage dans les mêmes conditions 3.0 France