Simulation

avec LTspice IV

Simulation

avec LTspice IV

Boucle à verrouillage de phase :

Etude de la PLL analogique, plages de capture et de verrouillage

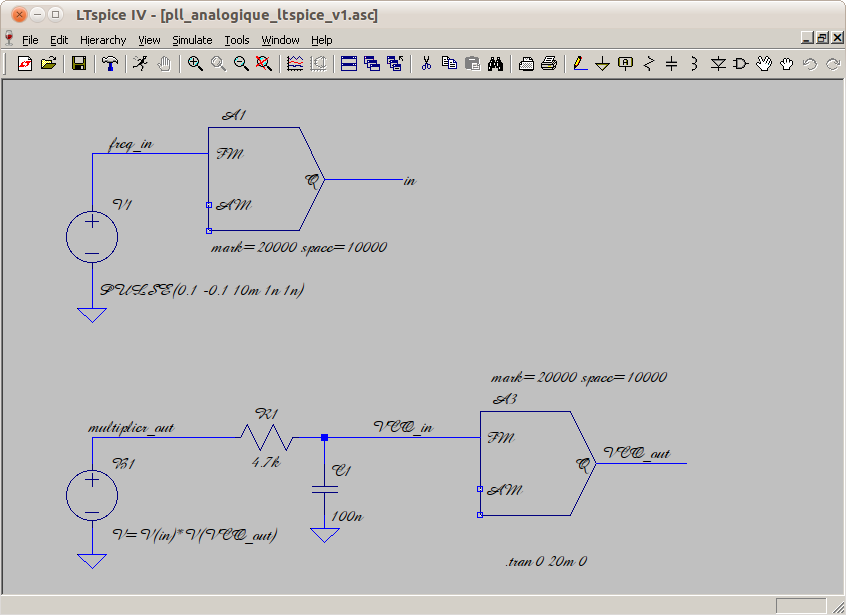

1. Saisie du schéma

Edit -> Component : modulate (VCO linéaire)

Value : mark=20000 space=10000

0 V donne 10 kHz

1 V donne 20 kHz

0,1 V donne 11 kHz

-0,1 V donne 9 kHz

-1 V donne 0 Hz...

La sortie du VCO est sinusoïdale (amplitude ± 1 V).

Edit -> Component : voltage (source de tension)

Value : PULSE(0.1 -0.1 10m 1n 1n)

Le signal d'entrée (Vin) est donc sinusoïdal, d'amplitude ± 1 V :

- fréquence 11 kHz de 0 à 10 ms (0,1 V en entrée du VCO)

- fréquence 9 kHz de 10 à 20 ms (-0,1 V en entrée du VCO)

La boucle à verrouillage de phase (PLL : Phase Lock Loop) est un

asservissement de phase.

La PLL est constituée de 3 éléments :

- un multiplieur (comparateur de phase)

- un filtre passe-bas (R1 et C1, constante de temps 0,47 ms)

- un oscillateur commandé en tension (VCO : Voltage Controlled

Oscillator)

Le multiplieur est obtenu de la manière suivante :

Edit -> Component : bv (arbitrary behavioral voltage

source)

Value : V=V(in)*V(VCO_out)

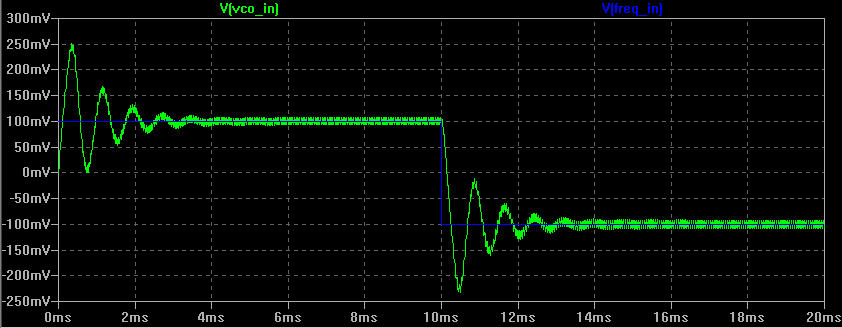

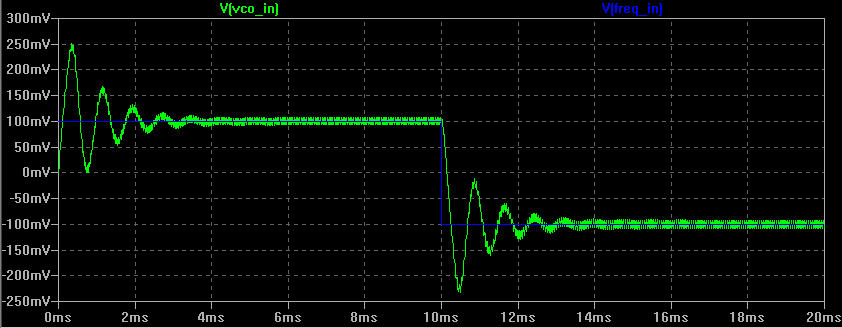

2. Simulation n°1a

Simulate -> Edit Simulation Cmd :

Transient : Stop Time : 20 ms

On lance la simulation (Simulate -> Run).

V(freq_in) donne l'image de la fréquence du signal d'entrée.

V(vco_in) donne l'image de la fréquence du signal de sortie de la PLL.

On voit que la PLL est accrochée et se verrouille pour f = 11 kHz.

A l'instant 10 ms, la fréquence d'entrée saute à 9 kHz : la PLL reste verrouillée.

On remarque que le régime transitoire dure environ 4 ms :

3. Simulation n°1b

On change les paramètres de la source de tension V1 :

Value : PULSE(0.3 0.1 10m 1n 1n)

On voit que la PLL n'accroche pas pour f = 13 kHz : la PLL fonctionne toujours à 10 kHz (free running frequency).

A l'instant 10 ms, la fréquence d'entrée saute à 11 kHz : la PLL est accrochée et se verrouille.

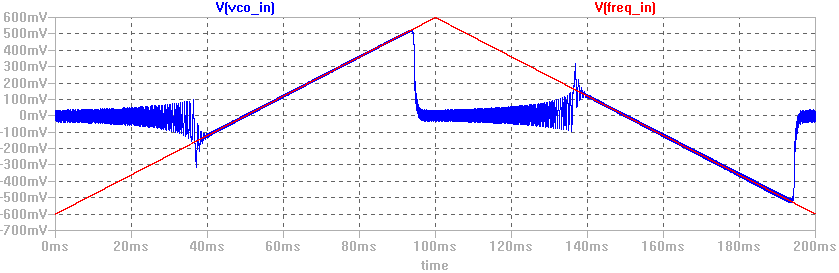

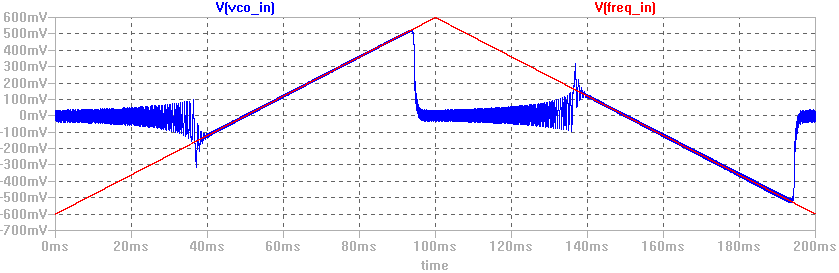

4. Simulation n°2

On change les paramètres de la source de tension V1 :

Value : PULSE(-0.6 0.6 0 100m 100m 1n)

La fréquence d'entrée augmente lentement de 4 kHz à 16 kHz puis diminue de 16 kHz à 4 kHz.

Au départ (4 kHz), la PLL n'est pas accrochée.

A 8,4 kHz (-160 mV), la PLL s'accroche.

A 15,2 kHz (520 mV), la PLL décroche.

A 11,6 kHz (160 mV), la PLL s'accroche.

A 4,8 kHz (-520 mV), la PLL décroche.

La plage de capture est donc : 8,4 kHz à 11,6 kHz

La plage de verrouillage est donc : 4,8 kHz à 15,2 kHz

Télécharger ces projets LTspice IV

(C) Fabrice Sincère ; Révision 1.1.3